Vhdl code for 3 bit ripple counter

We have detected your current browser version is not the latest one. Please upgrade to a Xilinx. Chrome , Firefox , Internet Explorer 11 , Safari. I have written this code.

This is showing the error when I try to synthesize: VHDL source expression not yet supported: The funny thing is that even if I entered empty code lines the tool still shows the error in line Even if the line 18 is empty. This problem is not occuring in any other code that I have written. As you said, I ran my file in a new project file and it was working. That problem did not show up. If the project file is corrupted how do I repair it? Also after running the attached RTL schematic showes up.

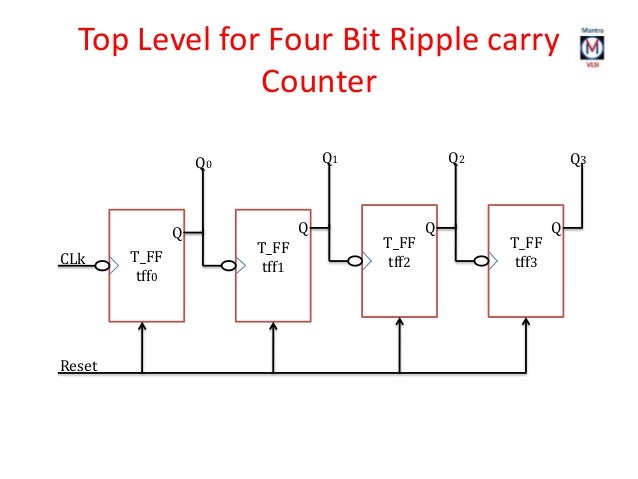

What's up with the lone counter below the and gate? There have been many schematics for other project files in which the connections were not shown completely. Why does that happen? If you take a look at the.

These scripts are able to regenerate a Project with all settings. Save a script once in a while and if your project file gets corrupted you can revive it with:.

That's because it is automatically generated and the programmers were too lazy or not paid to implement complex placement and routing functions. So the most simple way was chosen.

There are no connections missing they are just not drawn. Looks like a bug in the schematic display. Obviously the AND gate is for the counter rollover, which will likely be subsumed. Let's talk about your code.

Use signed or unsigned or natural or integer. In the case of the code you wrote, the following makes more sense:. I would generalize the counter, so you can count to any arbitrary value based on a generic, or whatever.

Usually, I give up and recreate the project. But before doing that, try to clean it. In the case of the code you wrote, the following makes more sense: I would also do that. But I have started VHDL a few days back.

Vhdl program for a 3 bit ripple counter using flip flops

Search Account My Xilinx Sign Out Sign in Create an account Language Toggle English Japanese Chinese Shopping Cart. All Silicon Devices Boards and Kits Intellectual Property Support Documentation Knowledge Base Community Forums Partners Videos. Applications Products Developer Zone Support About Search Language English Japanese Chinese. Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Reply Topic Options Subscribe to RSS Feed Mark Topic as New Mark Topic as Read Float this Topic for Current User Bookmark Subscribe Printer Friendly Page. Options Mark as New Bookmark Subscribe Subscribe to RSS Feed Highlight Print Email to a Friend Report Inappropriate Content. Message 1 of 13 16, Views. Hi, if it's not something simple Is this code your toplevel when you start XST?

Try to create a new project and synthesize your code there to see what happens. Message 2 of 13 16, Views.

Yes, I was running the code as the top module of my project. Message 3 of 13 16, Views.

No Idea how you might fix that. Message 4 of 13 16, Views. I tried the typecasting. The same error is still showing The same error is still showing.

[MOVED] verilog code for 3-bit synchronous counter

And in the same line Message 5 of 13 16, Views. Hi, project file corruptions happen once in a while, for whatever reason. So creating a new project will be the only solution for this. But you can help yourself by generating Tcl scripts through ISE. Save a script once in a while and if your project file gets corrupted you can revive it with: Precision RTL draws nicer schematics, but it's also costs a lot more.

Message 6 of 13 16, Views. Message 7 of 13 16, Views. Message 8 of 13 16, Views. Message 9 of 13 16, Views. How do I clean that? Message 10 of 13 16, Views. Download XilinxGo Mobile app. Privacy Trademarks Legal Feedback Supply Chain Transparency Contact Us.